To do List: Dig the Zaurus out of my "Sell on eBay" bin. Replace the battery (it only lasted 1/2 hour to begin with) Install a mouse driver Get a serial mouse connected and workingEnd goal: Use the Zaurus, directly mounted on the mouse, as video display/keyboard/mouse to interact with VNC running on the Zaurus to control my Mac.

Thursday, September 9, 2021

First Post for my RC2021/10 Entry

Wednesday, June 16, 2021

CMS 9619 Address Decoder Replacement

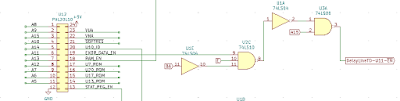

In my previous post on the MIKUL 6218 board, I mentioned that was using the lower 32K of address space on the CMS 9619 to swap in 16 banks of external RAM. You may remember that I had previously made some minor modifications on the CMS 9619 to use this space for an on-board 32K SRAM chip and still use the external I/O. What is happening here? Well, I had to remove all of my wire modifications to the CMS 9619, and restore it to the standard arrangement. With my new GAL programmer in hand, I figured out the logic equations to replicate the CMS 9619's U12 address decoder. I made an adjustment to how the U20 ROM/RAM socket and bus tranceiver are addressed so that I can have one GAL to have all 64K on-board and another for the standard external 32K. Now I can just swap out the GAL ICs to change the arrangement!

There is still a small glitch in UTIL_DECODE that I have to resolve (I think this is why CMS orginally used XOR logic PAL20L10 rather than the more common NAND logic PAL20V10), but everything seems to work great.

If you need a replacement decoder for your CMS 9619, or just want to make some modifications to the memory map, this is the way to do it!

MIKUL 1MiB Mods (continued)

With the virtual address jumper for the MIKUL 6218 sorted, I still needed to simplify the address decoding and memory chip selects so that 1 of the 4 SRAM sockets will be selected depending on the state of our virtual A19 and A20 addresses. Since the three I/O ICs (6522 VIAs) share the data bus with the memory, I also need to disable the memory when the I/O is active, and signal the GAL in U10 to select the appropriate 6522 VIA.

Fortunately, the CMS 9619 and 9639 use several signals (VMA, VUA, or UTIL_DECODE) to indicate when the processor board is addressing external memory or I/O. This greatly simplifies the decoding from the original MIKUL arrangment which had the GAL fully decoding all of the address lines from A6 through A15. But, since the MIKUL 6218 board does not use those CMS/EXORbus decode signals, I had to cut a few of the unneeded low address lines to the GAL and replace them. With this simplified arrangement, I had hoped to use a few standard 74LS logic ICs to select the RAM and I/O. But, after a few attempts reduce the number of logic chips I needed, I decided to bite the bullet and just get a GAL programmer.

Here is my new setup which seems to work great with macOS:

- XGecu TL866II plus USB programmer - programs the GAL

- minipro - reads and writes JDEC files to the TL866

- GALasm - turns logic equations into JEDEC file

Once I received a functioning programmer, I managed to get everything working well with my CMS 9619. So, now I can switch in 16 blocks of 32K RAM (512K) into the lower half of the CMS9619 address map, using the low nibble of its PIA output (at $FFC4) as a register to drive the virtual address lines. The CMS 9619 does not output a signal on its PIA for A20, so I can only use 2 of the SRAMs. Also, since the RAM addresses overlap the CPU addresses, half of each 512K SRAM chip can't be accessed (when A15 is high). This could be easily fixed by modifiying the U13 jumper board that I made previously, or even the CMS 9619 address decoder. Honestly, the original configuration was probably better for the CMS 9619 because it did not switch out the lower 8K of RAM that an OS would use. However, since my end goal is to use this with the CMS 9639 CPU and its integrated MMU, I will keep it as-is. I haven't fully tested the I/O and the VIAs yet, but I will get to those soon enough.

|

| 512K RAM on a MC6809! Note the rainbow virtual address jumper and the additional jumpers to route A19 and A20 |

More of the techincal details below, after the break...

Wednesday, April 21, 2021

MIKUL 1MiB Mods

A18 Addition

I really want to use my two 512KiB SRAM chips on this board to maximize the usable RAM. Fortunately, the MIKUL 6218 has 32 pin DIP sockets, so my SRAM physically fits. However, pin 1 (A18) of the socket is connected to VCC, limiting each socket to 256KiB (2^18) of memory. This is strange because four 256KiB (2MBit) SRAM chips would be perfect for this board (and my needs) but are quite unusual and are actually more expensive than four 512KiB (4MBit) SRAM chips.

To increase the socket capacity to 512KiB, the trace connecting A18 to VCC for each memory chip must be cut. Unfortunately, this is a wide power trace that is hidden under the end of the sockets. A few seconds with an 1/8" drill at a 45° angle cut through the A18 pull-up trace without too much collateral damage. Although I slightly cut into the socket, I barely avoided cutting into the next thin address line down.

|

| A18 to VCC severed. |

Then, I added a few wire jumpers to connect pin 1 of each socket to each other to give a common A18 line. This address line, along with A16 and A17, need to be connected to a new virtual address header. A19 and A20 will be connected from this header to a decoder to create the memory chip select signals.

Bank Address Eliminator

With the physical connections made, it's time to simplify the MIKUL 6218's memory bank select system.

This little jumper board just connects each real address to its respective memory address line (A11-A15), overriding the bank switching latch and logic at U13. The virtual addresses (A16-A20) connect to the 10 pin header which will connect to the main CMS 9639 processor board. The 3 pin header on the right will connect A19 and A20 to a decoder to select the correct memory chip.

With the RAM and this board in place and the virtual address lines pulled high, the board works exactly the same way as it did before and has the same memory map. However, the bank register functionality (which I could not test anyway) has been eliminated. But, without the virtual addresses, I can only access some of the RAM.

Next time ... the RAM chip select Decoder

Tuesday, February 2, 2021

CMS 9600A MPU Revival

I was recently able to trade one of my extra CMS 9619 SBCs for a CMS 9600A MPU (Thanks Joel!). This EXORbus processor card has very similar specs and layout to the CMS 9609 MPU card, but it uses the Motorola 6802 processor (an MC6800 with integrated RAM), rather than the MC6809.

If you are ambitious enough, you could even modify the CMS 9600A to use a MC6809 processor. Neither of these boards are as advanced as the CMS 9619 single board computer I have been working on, but nonetheless, I have been eager to get my hands on a MC6800 system to play with.

The board is in great condition, but had some areas of concern:

- There are no RS232 line drivers installed, instead using DIP program headers/shunts in their place.

- There is no boot or debugger ROM installed.

I mostly addressed the second concern before I even received the board. I OCR'd and transcribed the SYSMON debugger from the source code in the CMS 9600 manual (thanks for the scan Roland!). With a few adjustments, I was able to assemble it and format it for programing to EEPROM. Unfortunately, I could not get my AT26C16 EEPROMs to program in-circuit as I have for the AT28C64 EEPROMs. Anyway, I ended up using an adapter to use 1/4 of an AT28C64 EEPROM for testing.

As for the missing RS232 line drivers, this board was configured to use external line drivers on an RS232 breakout module (likely the CMS 9601-501). I tried connecting the appropriate serial lines directly to a TTL to USB serial adapter, but I did not receive any response from the board. I decided to just buy and install the line drivers to be consistent with my other CMS boards. This would eliminate a few variables while I focused on getting everything to boot from the EEPROM. Once I installed them it became clear that the new drivers were interferring with the baud rate generator due to an unusual wired jumper configuration that was causing contention. I removed some of the wire wrap jumpers so the settings are more consistent with my CMS 9609 board, and observed a nice clock signal arriving to the ACIAs.

Next, I added a small jumper to bring a constant 12V to the Power Failure Protect/Restart Circuit (connect 12V VIA to the "CR2" through-hole). Without it, the board stays in "locked reset" due to an assumed power failure.

While I was debugging these issues, I noticed a few distinct puffs of white smoke coming out of the CPU! I am not sure how that happened. I assume one of the address lines was pulled to ground through a test lead, but I was being quite careful. Anyway, with the CPU shot, I had to wait a few weeks for a replacement to arrive.

With a new CPU installed I was still troubleshooting with the logic analyzer when I noticed a column of asterisks in the terminal! I double checked the manual and realized that the monitor had been prompting me for a command for several reboots!

*V

FROM ADDR FF80

FF80 04 48 49 4E 5A 56 43 0D 0A 15 00 04 0D 0A 42 4B

.HINZVC.......BK

FF90 41 44 44 20 04 0D 0A 46 52 4F 4D 20 41 44 44 52

ADD ...FROM ADDR

FFA0 20 04 0D 0A 54 48 52 55 20 41 44 44 52 20 04 54

...THRU ADDR .T

FFB0 4F 20 41 44 44 52 20 04 56 41 4C 55 45 20 04 4D

O ADDR .VALUE .M

FFC0 FA 42 45 F8 9B 47 F9 14 52 F9 35 54 FA A2 48 F9

.BE..G..R.5T..H.

FFD0 B7 56 FD DD 49 FA 07 4A F9 FD 46 FA 67 51 F8 1C

.V..I..J..F..Q..

FFE0 44 FA 9D 4B FA B4 31 F9 00 32 F8 EF 4C F8 1C 53

D..K..1..2..L..S

FFF0 F8 1C 4F F9 B6 4E F9 B8 F8 4F F8 59 F8 54 F8 00

..O..N...O.Y.T..

Once I knew that everything was working, I took another stab at programming the EEPROMs in-circuit. After some jumper configuration changes on my CMS 9619A, I was finally able to program a few 28C16 EEPROMs. As it turns out, the CMS 9609 has some timing differences from the CMS 9619 that apparently prevent it from programming the EEPROMs. But with the CMS 9619 configured to accept the smaller 24 pin 28C16 EEPROM, the programming worked fine.

With everything else up and running, I wanted to try a TTL level USB/serial connection using the board's original DIP program headers, rather than the RS232 drivers that I added. Following the manual, it was easy to swap out the drivers and connect it up:

PHEW!

Sunday, January 3, 2021

MIKUL 6218 Memory and VIA EXORbus board

I haven't spent much time working on my CMS 9639 SBC because, unlike the CMS 9619, it does not have any usable on-board RAM and does not include a monitor/debugger in ROM. Instead, it is designed to use an external memory board (which I don't have) on a back plane (which I now have) and boot OS-9 from a disk drive (which I don't have). What is nice about the device is the built-in memory manager which uses up to 1MiB of RAM. Unfortunately, EXORbus RAM cards are still prohibitively expensive on eBay and only have 16K to 64K of RAM capacity. Since the components would be far less than the price of those boards, I took a stab at designing a 1MiB SRAM board with a bonus additional I/O expansion.

I had just started to get components inserted into an EXORbus prototype board when I noticed the MIKUL 6218 Memory and VIA boards appearing on eBay at reasonable prices (<$45 shipped). Let's take a look at the board:

Click below for more details...

Wednesday, December 16, 2020

NitrOS-9 boot from ROM

One of the shortcomings of this CMS 9619 system is the fairly complicated OS9 bootstrap procedure I had to use in the absence of any sort of disk drives. To summarize:

- DEBUG19 (in ROM) starts

- Host computer transfers a small loader program using DEBUG19's memory edit routine

- DEBUG19 jumps to the loader program, loading the kernel track from the drivewire server and runs it

- NitrOS-9 starts and continues loading the rest of the bootfile from drivewire

- 8K of address space is taken up by DEBUG09 ROM

- The host computer needs a separate script to efficiently transfer the loader program using DEBUG19

- 2 x 256 byte blocks of RAM need to be reserved to hold the RAM interrrupt vectors and data for DEBUG19

I had hoped that the kernel file could run from ROM and directly load disk images from drivewire. Unfortunately, the NitrOS-9 code is tied closely to the CoCo's hardware, and always relocates the kernel from ROM to RAM. To combat this problem, I replaced NitrOS‑9's relocation routines and added a module to initialize the CMS 9619 hardware for booting directly into the NitrOS-9 kernel. From there, the NitrOS-9 booter (on ROM) will load a disk image over drivewire. This is very similar to the set-up for the CMS 9639 (and I assume other computers sold with OS9).

NITROS9 ROM BOOT

NitrOS-9/6809 Level 1 V3.3.0

CMS 9619A

(C) 2014 The NitrOS-9 Project

** DEVELOPMENT BUILD **

** NOT FOR DISTRIBUTION! **

Wed Dec 16 16:07:07 2020

http://www.nitros9.org

* Welcome to NitrOS-9 Level 1 *

* on the CMS 9619A ASBM *

yyyy/mm/dd hh:mm:ss

Time ? 2020/12/12 05:55:55

>> Clock Initialization Errors <<

December 12, 2020 05:55:55

Shell

OS9:

(The Clock init Error is because the code currently expects the DEBUG19 clock setting routines to be installed in ROM, which they are not. I still need to add these.)

It took some careful configuration to ensure that the CMS 9619 can boot from the DEBUG19 loading process OR directly from ROM, with no wasted memory in either case. Since the final NitrOS-9 boot ROM is less than 4K in size, an abbreviated DEBUG19 can also be programmed into the EEPROM. The code is available on Github.

On the note of programming EEPROMs, I discovered back when I was disassembling DEBUG19 that I can use DEBUG19's memory edit routine to program an EEPROM on the board. Of course, the timing is all wrong and the editor returns an error because the EEPROM takes much longer to store the value than RAM would. With some help from an expect script, it is fairly easy (though slow) to continuously run the memory edit routine, once for each byte, and ignore the errors. So, I can program EEPROMs on board by simply moving a jumper and running the script. If anybody has one of these boards without a ROM, I would be happy to send you a fully programmed EEPROM with NitrOS-9 and DEBUG19. In fact, I think I will add that to my tindie store soon!

Friday, October 23, 2020

Never Valid User Address

After finding out that my CMS 9619 Advanced Single Board MicroComputer was having problems accessing the EXORbus, I tried some trouble shooting. My MULTI-PLANE EXORbus backplane made it easy to accesss the various signals with an extra card edge receptacle attached. I tried pulling down various lines of the data bus with a resistor, and noticed that the 8 bits of data seemed to be responding appropriately. So, probably not the data bus tranceiver.

With little more to go on, I ended up buying an inexpensive USB logic analyzer and installing PulseView software for it. I was quickly able to identify that the bus's VUA (Valid User Address) signal was not rising when it was supposed to, even though it was receiving the correct signal from the PAL address decoder. Without this signal, the I/O card was never properly addressed, and the data bus was always floating. I tested another CMS 9619A board I have which displayed similar symptoms and found that it too was suffering from a failure of the same IC. Odd coincidence. So, after some desoldering, super-gluing a trace that was inadvertently partially pulled off the board, and re-soldering a new 74LS244 8-bit driver (U9), I am back in business. The chip came off of the other board much easier with the help of a heat gun.

I can't recommend these cheap logic analyzers enough to a hobbyist, although the first one I recevied was not working properly on some channels (make sure to test them before you rely on them for anything).

I also bought an EspoTek Labrador USB oscilloscope to try out, but I received, tested, replaced, and finally used the cheap logic analyzers from ebay while I was still waiting for the Labrador to arrive.

Thursday, October 8, 2020

CMS 9619 Hardware Mods (continued)

Update: Since this post I have figured out how to change the address map using a GAL IC.

I recently posted some minor hardware modifications I made to my CMS 9619A Advanced Single Board Microcomputer to get it to use a 32K SRAM chip. Unfortunately, I had to disable the EXORbus data bus transciever to get it to work. So, although the board works properly as a single board computer, it cannot access the EXORbus. With NitrOS-9 up and running, I would really like to regain the ability to use external I/O cards.

To get this to work, the data bus transceiver (U11) needs to be re-enabled, but only during the External I/O address space at $FF80 to $FFBF (checkout the CMS 9619 memory map for details). This can be done by combining the normal data bus transceiver enable signal with the signal for address line A15. This works because the only time the transceiver is normally enabled in the high address space is in the External I/O address space (because everything else in that range is onboard the CPU module). All we should need to do is invert the normal data bus transceiver (U11) enable signal, and NAND it to the A15 address line.

Fortunately, there are a few ICs on the board that are not fully utilized. We can use the 1st gate (pins 1->2) on the U1 74LS04 inverter IC to invert the data bus transceiver enable signal, and the first gate (pins 1+2->3) on the U3 74LS00 gate IC to NAND the inverted signal to A15.

This is almost too perfect that these logic gates are available, so I'm sure it won't work. Also, since the board is already bodged in this area with the factory's dead-bug'ed delay line, all of the modifcations are easily reversible with no traces to cut.

|

| Before |

|

| After |

After the modifcations, everything booted up properly and I was able to access my 32K SRAM at $0000-$7FFF However, I was unable to read any data from my known-good CMS 9650 8 port Serial I/O card. After some basic troubleshooting, I got to thinking... I don't think this processor card was EVER able to access the external bus- which is why I think I chose it for modfications. Major troubleshooting to come...

Wednesday, September 30, 2020

CMS 9619 Drivewire Boot to NitrOS-9

Friday, September 25, 2020

Monday, June 1, 2020

RC2020/04 Finale and Wrap-up

After getting OS9 to boot to the shell on my CMS 9619 SBC, I was hopeful to get the DriveWire module working to load in disk images in a more intuitive way. I don't have an extra RS232 to USB adapter currently available to me, so I tried using a USB to TTL level serial adapter on the board's peripheral port connected to the MC6821 PIA. Using the DriveWire module intended for use with the Tandy CoCo's serial "bit-banger" port (also connected to a MC6821 PIA), I was hopeful that I could get things running. Unfortunately, I am pretty sure I am having some sort of baud rate mis-match. The module issues a single character (probably indicating an INIT), then everything is stuck. I am not totally sure what baud rate I should use since my board is running at 2 MHz, compared the the Coco's 0.89 MHz. I think that is probably a lost cause without significant modifications to the timing in the software. (Actually, 57600*(2/0.895) ≈ 128000, a standard baud rate. I will give this a try...)

Once I get my other RS232 to USB adapter, I should just be able to run it off of the serial port, without any bit-banging related timing issues.

RC2020/04 Wrap-up

So, I am fairly happy with my progress this RetroChallenge, despite having to move to a new house. The extra month certainly helped. I was able to:

- Make some hardware modifications on my CMS 9619 to get enough on-board RAM to run OS9 (Part 1, Part 2)

- Get OS9 booted to the shell on the CMS 9619

- Order my EXORbus backplane card design (Part 1, Part 2).

Once I get the rest of my supplies out of storage, I will get some of the backplanes on tindie for purchase.

Thursday, May 28, 2020

Monday, May 18, 2020

EXORbus ATX Power Backplane Ordered!

Thursday, April 23, 2020

OS9 shell on a real CMS 9619!

I finally got it working thanks to the advice of a kind member of the Tandy Color Computer (CoCo) discord channel. Interrupts! Once I connected the 6551 ACIA's IRQ line to the 6809's IRQ (using the CMS 9619's TS8 jumper block), the OS9 shell came alive:

You can see the system start up with the ROM's "DEBUG19" prompt. Then it proceeds to:

- clear some memory

- use the edit memory command to enter in the ZMODEM program and a mini boot-loader

- jump to the boot-loader to get the first part of the kernel into memory sector by sector from a disk image

- jump to the NitrOS9 Kernel.

- The kernel starts loading in more sectors using its ZMODEM boot module, until it finally runs the terminal shell and gives me an "OS9:" prompt.

And now, with interrupts enabled, the shell responds! Now I need a proper ZMODEM file manager to load in and run other programs.

Tuesday, April 21, 2020

Fortunately... Unfortunately...

|

| Filled up Sockets! This would have cost many hundreds of dollars back in the day. |

Fortunately, this particular type of gibberish is recognizable as a baud rate mismatch, which makes sense. NitrOS-9 uses a completely different system for getting the baud rate than the CMS 9619 uses. After an adjustment to the terminal description files, I had an improvement:

YES! I was so excited until I hit the return key and... nothing. It does not respond with another prompt or an error or anything. Just stuck. More work to do...

Saturday, April 18, 2020

Interru(o)ptions

This post is just to document and explore some of the interrupt options on the CMS 9619 that could be compatible with NitrOS-9's interrupt requirements (60Hz based on VSYNC).

RTC-58323 Real Time Clock

The CMS 9619's RTC can output a standard clock signal. The CMS 9619 has jumper block (TS10) that allows you to select a signal to connect to the Control B input (CB1) on PIA0. The signals are:

- 1 hour

- 1 minute

- 1 second

- 1024 Hz

1024Hz seems too fast and 1Hz is too slow for the interrupt we need. But, it's nice to know it is there. Probably better for a watchdog timer.

MC6840 Programmable Timer Module

The MC6840 timer in the CMS 9619 can generate a continuous square wave from 1MHz (1/2 the system clock speed) to about 141 years. The MC6840 can generate an interrupt every low transition of the output, or any of outputs can be jumped to the Control A input (CA1) on PIA0 using the CMS 9619's TS14 jumper block. I am not sure why there are 2 options to generate the interrupt here though.

To get an approximately 60Hz signal, I need to configure the MC6840 with a $4000 (16,382) divider of the system clock (1/((16,382+1)(2E-6)*2) = 61.03Hz). This should be easy to configure in the MC6840 16-bit Continuous Operating Mode.

Using the MC6840 PTM with a jumper wire to the right side of the TS10 jumper block (at the RTC), which connects to the MC6821 PIA's CB1 seems like the most suitable choice. It is almost identical to NitrOS-9's standard VSYNC interrupt on the CoCo's PIAO CB1 so I can re-use most of the code, and seems highly configurable.

External Circuit

The MC6840 Application Guide contains a circuit for getting a 60Hz TTL signal from the 120V power lines. I think this signal could work as a trigger to the MC6840 or the MC6821 PIA. However, it is overly complicated for this project, which does not need exact long-term timing.

Aside

I spent some time watching the "Virtual" CoCoFEST for inspiration today. Check it out!

Friday, April 17, 2020

Kernel of Truth

I spent some time today trying to get NitrOS-9 booting on the CMS 9619 SBC. I was able to get this working in emulation, so I was hopeful that it would be an easy job with real hardware. After some minor modifications to deal with timing in the slower environment, the ZMODEM module is working perfectly! However, getting NitrOS-9 running has been much more complicated.

As part of the boot process, NitrOS-9 relocates the kernel "disk" sectors from $2600 to high memory. Memory was cheap with my 6809 emulator, so everything that is not ROM was configured as RAM. The emulator easily relocated the kernel to $C000-$Dxxx, just below the main debug ROM at $E000-$FFFF. On my real board, that address range is not populated with RAM, so, I was relocating the kernel into thin air! I changed the load area to $7000-$8xxx, but had a problem because the relocation routines expect the video buffer at $8000, and over-write part of the kernel. I could keep toying with the relocation routines, but I think I just need to get more SRAM to populate the empty ROM sockets. I just put an order in, and am hoping for for some new 8K SRAM ICs by the end of next week.

Thursday, April 9, 2020

CMS 9619 Hardware Mods

|

| Note the 5 28 pin sockets on the right side of the board for 4K or 8K SRAM or ROMs |

In order to get NitrOS-9 running on my CMS 9619 SBC, I am going to need a lot more RAM. This board is configured to have up to 8K of onboard RAM and 32K of onboard EPROM, with options to use 4K or 8K chips. 32K and 64K RAM expansion boards were available in several configurations, including battery powered non-volatile SRAM to retain state during power off. Unfortunately I haven’t seen any of these available at a decent price, so expansion boards are not a good option for me. I do have a 32K SRAM chip with a similar pin-out (part of an eBay Dragon 32 IC kit) to the 8K module which would fit nicely.

My board already has 8K of RAM installed in socket U34 ($8000-$9FFF), and 8K of ROM in socket U7 ($E000-$FFFF). Socket U20 is not selected by the PAL decoder on this particular board, either by design (being configured for 1 x 8K DIP SRAM vs. 2 x 4K SRAM) or due to some problem with the PAL. My new 32K SRAM needs to be selected and addressed, which requires some minor modifications to the board.

To select the new 32K RAM chip, I first raised pin 16 of the PAL decoder IC normally responsible for enabling the U20 RAM socket (apparently not working on my board). Once that was done, I used the A15 address signal to enable U20 socket instead. This required a short jumper wire from pin 3 (A15) to pin 16 (U20 CS') across the PAL address decoder. So now, whenever the A15 line is low ($0000-$7FFF), the SRAM in U20 will be enabled. This is perfect since the SRAM IC is 32K, and will fill the bottom half of the board's address space.

To address all 32K of the SRAM, I first cut the GND signal from pin 1 of the U20 socket. This is tricky since the trace is right against the socket. I ran a jumper from pin 5 of the PAL decoder to pin 1 of the U20 socket (A14). Then I set the jumper at TS19 to connect pins 2 and 3 (A13), and the jumper at TS6 to connect 8 and 10 (A11). Socket U20 now has the address lines it needs to decode all 32K of memory.

|

| Two long jumpers to connect A13 (I realized later this is handled by jumper TS19) and A14, and one short jumper for A15 |

I was hopeful that everything would just work with the modifications, but of course it wasn’t that easy. The problem has to do with the data bus transceiver (U11) on the board. It is driving “data” from the EXORbus onto the processor data bus in the address range of the new RAM. However, there isn’t anything on the bus to drive and it is just causing contention with the new SRAM. For now, I disabled the transceiver by disconnecting the dead-bug'ed delay line from the enable pin (pin 19) of the transceiver, and pulled that enable pin high with a short jumper wire to Vcc. This isn’t ideal because it disables all of the external bus, including the I/O address range in addition to the low memory range that we need. So right now the CMS 9619 can’t read anything else on the EXORbus.

|

| Short jumper to disable the EXORbus data bus transceiver (U11) |

So, with 40K of RAM (8K in U and 32K in U20), and 8K of ROM with sockets for another another 16K, the board is nicely outfitted to run some real programs.

Tuesday, April 7, 2020

RetroChallenge 2020/04 is here!

I'm starting a bit late, but since I am in quarantine and working on some old computer stuff anyway, why not enter?! Here are my goals for RetroChallenge 2020/04:

- Get my ZMODEM NitrOS-9 boot-loader working on real hardware.

- Work on my fork of an Apple II SD card reader, using retro hardware.